こんにちは。量子研究所の赤星です。 今回は、2024年9月15日から20日にかけてカナダのモントリオールで開催された国際会議IEEE QCE24(https://qce.quantum.ieee.org/2024/)の参加報告と、 そこで発表した内容を含めた最近の研究成果についてご紹介します。

IEEE QCE24 参加報告

概要

IEEE QCE24 (IEEE International Conference on Quantum Computing and Engineering 2024、別名IEEE Quantum Week 2024)は、IEEEが主催する年一回の量子計算技術に関する国際会議です。

2024年度はカナダのモントリオールで現地開催(講演はハイブリッド)され、約一週間にわたって量子計算のハードウェアからソフトウェア、アルゴリズムに至る非常に幅広い分野の発表が行われました。

今年度の参加者は58か国から約1550名ということで、非常に大規模な国際会議です。

期間中は学術的な発表に加え、量子技術を手掛ける企業の展示ブースも設けられており、量子計算ならではの学術・産業双方のコミュニケーションが活発に行われておりました。

今回私は、現在携わっている研究に関するポスター発表と富士通展示ブースでの説明員、そして業界の動向をつかむための聴講を目的とし、全日程に参加してきました。

企業展示ブース

富士通展示ブースでは、ハードウェアの取り組みとして理研RQC-富士通連携センターで研究開発中の超伝導64量子ビットチップおよび

デルフト工科大と共同で研究開発中のダイヤモンドスピン量子コンピュータのモックアップ模型の展示を行い、

さらにソフトウェアの取り組みとして独自量子計算アーキテクチャ(STARアーキテクチャ)、

高速量子計算シミュレータ (DD simulator)、

Computing Workload Broker (CWB)のスライド展示が行われました。

ブースは企業展示フロア入り口の目の前ということもあり、多くの方に訪問してもらうことが出来ました。

GoogleやMicrosoftなどの名だたる企業も展示を行っている中、存在感を示すことが出来たと思います。

ポスター発表

富士通からは、米国富士通研究所のメンバー含め4名の研究員が技術論文セッションやワークショップで口頭発表を行い、私がポスター発表を行いました。 ポスター発表では、近年我々が提案した独自の量子計算アーキテクチャ(STARアーキテクチャ)の効率的な実行に必要となるソフトウェアについて発表を行いました(技術的な内容は後半に概説)。 ポスター発表は複数日程に分かれており、また会場は企業展示ブースの奥にあったこともあり、人が集まりにくいという問題点もありましたが、多くの方に訪問していただくことが出来ました。 特に嬉しかったのは、STARアーキテクチャの存在を知ったうえで、我々のポスターを目指して訪問してくださる方や、以前参加した国際会議で知り合いになった方が訪問してくださったりしたことです。 昨年度参加した国際会議ではそういったことはなかったため、この1年間で我々の研究成果の認知度が着実に高まってきていることを感じました。

業界の動向まとめ

QCE24では、多くの有名企業のkeynote発表や、様々なテーマに沿った発表をまとめたワークショップが開催されました。 私は量子エラー訂正(詳細は後述)に関連するトピックの発表を聴講しましたが、まず感じたのは量子エラー訂正の実現に向けた技術の着実な進歩です。 特に注目されていたのは、MicrosoftとQuantinuumが最近発表したイオントラップ方式を用いた量子エラー訂正実験[1] と、Googleによる超伝導方式を用いた量子エラー訂正実験[2]の成果でした。 特にGoogleの成果は、量子エラー訂正を用いることでエラー率が低減することを確認し、かつ量子エラー訂正を量子計算中に実行するために必須の技術であるリアルタイム復号も実装しており、 量子エラー訂正を用いた量子計算の実現を予感させる重要な結果です。 IBMも独自の量子エラー訂正符号[3]の実装に向けたハードウェア開発を進めており、必要なスペックを持つ小規模プロトタイプの開発に成功したとコメントしていました。 これらに加え、量子エラー訂正処理を高速に実施するための実装(FPGAの活用)の検証を行っているグループも複数あり、実デバイス上での量子エラー訂正に向けたノウハウが着実に蓄積されていると感じました。 今回発表されていたような実験結果に触発され、今後は量子エラー訂正の理論と実際のデバイスを組み合わせた実験がますます増えていくことと思います。 富士通としても、今後世界的なプレゼンスを高めるために、ハードウェアとソフトウェア両者の研究開発を行っている強みを生かし、欧米の有名企業に負けない成果を出していく必要があると感じました。

最近の研究成果

次に、今回のQCE24でもポスター発表やブース展示を行った、私が携わっている最近の研究成果について紹介します。

背景

量子コンピュータは、古典コンピュータと異なり、0と1の「重ね合わせ状態」を取ることが出来る「量子ビット」という基本単位で計算を行うコンピュータであり、この量子特有の「重ね合わせ状態」を活用することで、一部の計算タスクに対して劇的な高速化を実現すると期待されています。

しかしながら「重ね合わせ状態」は非常に脆く、容易に壊れてエラーを起こしてしまいます。

そのため、現在一般に公開されている数十から数百量子ビット規模の量子コンピュータ(いわゆるノイズ有り中規模量子コンピュータ、略してNISQ)では、エラーの影響により将来的に期待されるような複雑な計算タスクを実行する事は困難です。

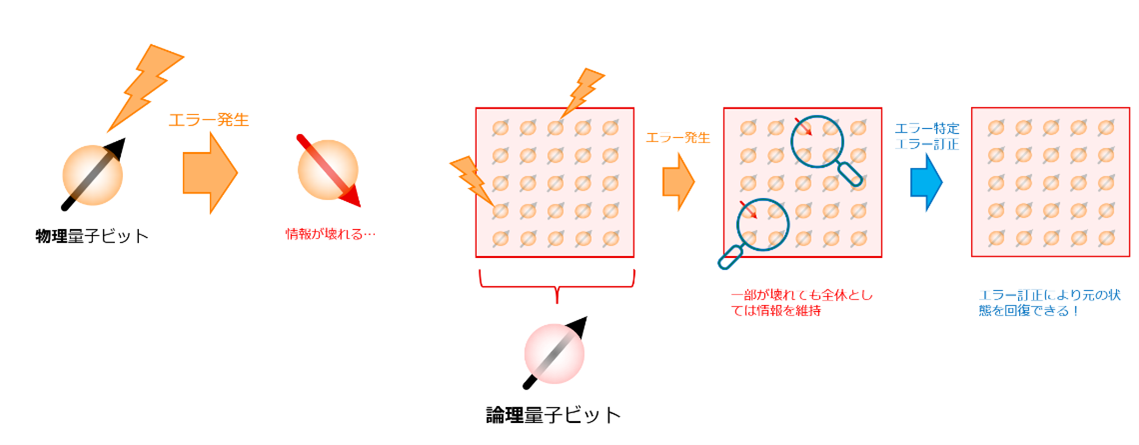

一方で、このようなエラーは、既に言及している量子エラー訂正という技術を用いることで抑制することが可能であることが理論的に証明されています(図3)。

この実現に向け、先述のような量子エラー訂正実験が世界の名だたる企業・研究機関で精力的に研究されているわけですが、量子エラー訂正を行いながら計算を実行する誤り耐性量子計算(略してFTQCと呼ばれる)には、

それはそれで非常に大規模な量子コンピュータ(典型的には数百万量子ビット規模)が必要であると考えられており、いかにその必要リソースを削減するか、が量子コンピュータ研究の主要な研究テーマのひとつとなっています。

STARアーキテクチャ

このような背景のもと、我々量子エラー訂正の研究グループでは大阪大学の藤井啓祐教授との共同研究により、より少ないリソース規模で有用な量子計算タスクを実行できると期待される、独自の量子計算アーキテクチャ(STARアーキテクチャ)を提案しました[4]。

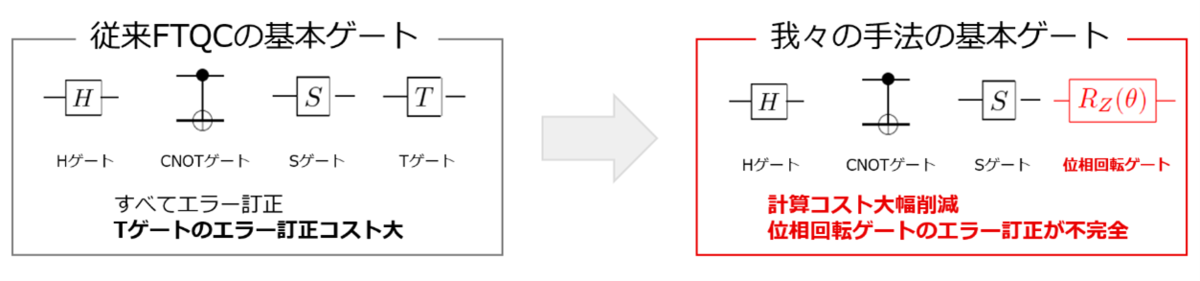

そのアイデアを図4に示します。

一般にFTQCでは、基本ゲートと呼ばれる4種類の量子ゲート操作を組み合わせることで任意の計算ができることが知られています(図4左、古典コンピュータにおける基本論理ゲートと同様の役割)。

我々は、この基本ゲートのうち、特に量子エラー訂正に大きなコストがかかるTゲートを別の量子ゲート(位相回転ゲート)に置き換えることで、その部分にかかる必要リソースを大幅に削減するというアプローチをとりました(図4右)。

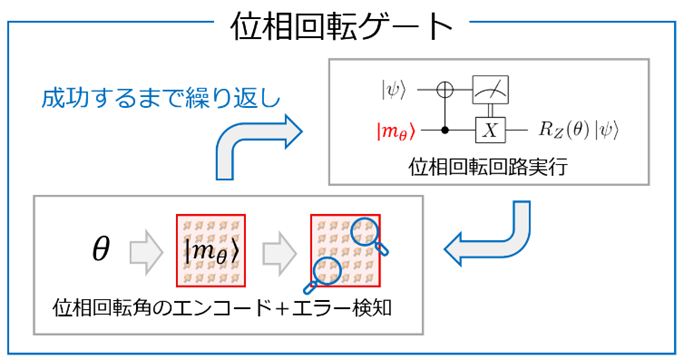

位相回転ゲートは、①位相回転角のエンコード、②それを消費する位相回転回路実行、という2ステップで実行されますが、両者とも一定確率で失敗するため、この2ステップを成功するまで繰り返します(図5)。

リソース削減のトレードオフとして、位相回転角のエンコード時に一部取り除けないエラーが残ってしまうのですが、独自設計したエラー検知方法を導入することで、高い精度を維持したまま効率的に位相回転ゲートを実行できる方法を構築することに成功しました。

最近の進展:精度改善と実用タスクにおける量子加速の可能性

最近では、元々の提案手法からさらに進展し、位相回転ゲートの精度改善が行われました[5]。この方法では、位相回転角のエンコード方法が改良されており、結果として回転角が微小な場合に劇的な精度改善を達成しています。微小な回転角の位相回転ゲートは、量子コンピュータの有望な応用先である材料物性シミュレーションや化学物質シミュレーションに現れるものであり、こうした計算を既存技術よりもさらに省リソースで実行できると期待されます。

また、STARアーキテクチャを用いて高速な計算を実行するには、先述の基本ゲート操作を漫然と行うだけでは不十分であり、例えば先述の位相回転角エンコード時のエラー検知プロセスに伴うオーバーヘッドをいかに軽減しながら実行するか、といった課題も解決する必要があります。我々はそうした効率的な回路実行を実現するソフトウェアの研究開発も行っており、今回のポスター発表ではその実装内容を紹介しました。

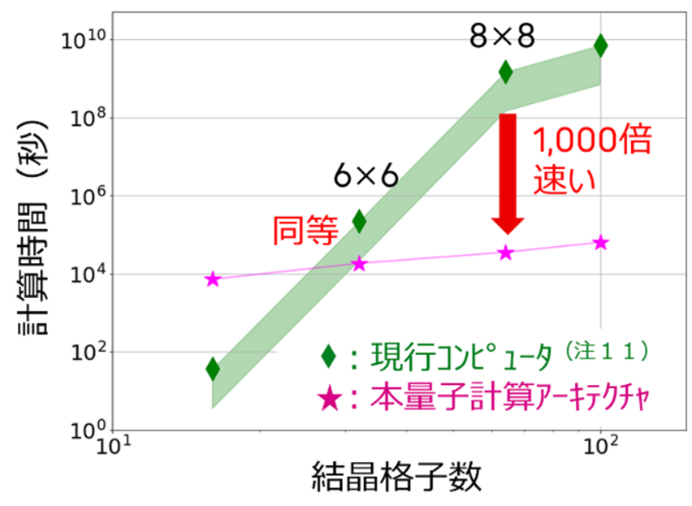

その中で用いられている最適化技術を用い、近い将来重要と期待される物性モデルのシミュレーションを題材に、最終的にどれくらいの規模の量子コンピュータでどのくらいの速度の計算ができるかを理論的に見積もると、6万量子ビット規模のデバイス上で、古典コンピュータよりも1000倍程度高速な計算が実現可能という結果を得ました[6](図6)。この結果は、実用的な量子計算が従来の想定よりも早く実現できる可能性を示唆しています。

上記の精度改善と物性モデルシミュレーションのリソース見積もりについて詳しい内容にご興味のある方は、プレスリリース[7]や原著論文[5,6]をご参照ください。

おわりに

国外で開催される国際会議参加は今回が入社してから2回目でしたが、特に規模の大きい会議だったこともあり、良い経験になりました。 特に印象に残っているのは、やはり海外企業などの研究開発のスピード感と研究者の層の厚さです。今後は実機検証の重要性がさらに高まり、競争が激化していくと思います。 そういった中で、富士通もハード・ソフト両面を研究していることを活かし、さらに成果を出していくことが必要です。 今後も富士通の量子業界におけるプレゼンス向上に貢献できるよう、精進していきたいと思います。

最後までご覧いただき、ありがとうございました!

参考文献

[1] Ben W. Reichardt et al., arXiv:2409.04628 (2024) https://arxiv.org/abs/2409.04628

[2] Google Quantum AI, arXiv:2408.13687 (2024) https://arxiv.org/abs/2408.13687

[3] S. Bravyi, et al., Nature 627, 778-782 (2024) https://www.nature.com/articles/s41586-024-07107-7

[4] Y. Akahoshi et al., PRX Quantum 5, 010337 (2024) https://journals.aps.org/prxquantum/abstract/10.1103/PRXQuantum.5.010337

[5] Toshio et al., arXiv:2408.14848 (2024) https://arxiv.org/abs/2408.14848

[6] Y. Akahoshi et al., arXiv:2408.14929 (2024) https://arxiv.org/abs/2408.14929

[7] プレスリリース記事